Graduate School Form 9

# PURDUE UNIVERSITY GRADUATE SCHOOL Thesis Acceptance

| This is to certify that the thesis prepared                                                                    |

|----------------------------------------------------------------------------------------------------------------|

| By Randall James Fisher                                                                                        |

| Entitled General-Purpose SIMD Within A Register: Parallel Processing On Consumer Microprocessors               |

| Complies with University regulations and meets the standards of the Graduate School for orginality and quality |

|                                                                                                                |

| For the degee of Doctor of Philosophy                                                                          |

|                                                                                                                |

| Signed by the final examining committee:                                                                       |

| (C-, chai                                                                                                      |

| lech H James - Co- Chair                                                                                       |

| Ewhal Ill                                                                                                      |

| Zhing Zi                                                                                                       |

| Approved by: Department Head Date Jan. 30, 20,                                                                 |

| is This thesis is not to be regarded as confidential.                                                          |

|                                                                                                                |

| Format Approved by:                                                                                            |

| Chair, Final Examining Committee or Thesis Format Advisor                                                      |

# GENERAL-PURPOSE SIMD WITHIN A REGISTER:

# PARALLEL PROCESSING

ON

# CONSUMER MICROPROCESSORS

A Thesis

Submitted to the Faculty

of

Purdue University

by

Randall James Fisher

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2003

UMI Number: 3108343

#### **INFORMATION TO USERS**

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 3108343

Copyright 2004 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# In memory

of my father, Robert, who sparked and supported my interests in many things, and my grandmother, Ethel, who helped me find beauty in the world around me.

I miss you both very much.

For Shelbi and Bobby, and the rest of my family and friends

#### ACKNOWLEDGMENTS

I would like to thank my committee: My adviser, Hank Dietz, for his guidance and for keeping things interesting; his co-chair, Leah Jamieson, for stepping in when she really had more than enough things to worry about; and Ed Delp and Zhiyuan Li for their patience and support. I would also like to thank the ECE graduate coordinator, Daniel Elliott, for the same.

I would also like to thank several people for their assistance in this research and preparation of this dissertation. Tim Mattox always provided a willing sounding board, as did my other colleagues, Soohong Kim, Gayathri Krishnamurthy, Ray Hoare, Ekechi Nwokah, Will Cohen, and Rick Kennell (I apologize if I have misspelled anyone's name). Rick was also helpful during the preparation of this document. Matt Golden was especially helpful with bureaucratic matters, as was Andy Hughes with formatting and procedural issues.

Dondi Bogusky deserves special recognition for allowing me to talk him into putting Linux on the G4 system in his office so that I could use it. My sister-in-law, Rhonda, also deserves credit for her help with Internet access and for providing caffeine over the summer.

I would especially like to thank Ed Bos, without whose help I would not have made it through my undergraduate years, and Tom DeMarse, who kept me sane during my years at Purdue. Of course, it was his fault that I came here to begin with. I would also like to thank all the other friends I have made at Michigan State and Purdue for, well, for being my friends.

Finally, I would like to thank my mother, Merrill, and my brother, John, for their love and support throughout my college career and life.

# TABLE OF CONTENTS

|    |      |         |                                                | Page |

|----|------|---------|------------------------------------------------|------|

| LI | ST O | F TAB   | LES                                            | viii |

| LI | ST O | F FIGU  | JRES                                           | . x  |

| N( | OME  | NCLAT   | URE                                            | . xi |

| ΑI | BSTR | ACT     |                                                | xii  |

| 1  |      |         | 1                                              |      |

|    | 1.1  | Motiva  | ation                                          | . 1  |

|    |      | 1.1.1   | A Brief Introduction to Processing Models      | . 1  |

|    |      | 1.1.2   | Multimedia Extensions                          | . 6  |

|    |      | 1.1.3   | My Thesis                                      | . 8  |

|    | 1.2  | Relate  | d Work                                         | . 9  |

|    |      | 1.2.1   | Software-only Methods                          | . 10 |

|    |      | 1.2.2   | Non-compiler Tools                             | . 12 |

|    |      | 1.2.3   | Libraries                                      | . 13 |

|    |      | 1.2.4   | Compiler Support for SWAR                      | . 14 |

|    |      | 1.2.5   | Summary                                        | . 25 |

|    | 1.3  | Scope   | of Work                                        | . 27 |

|    | 1.4  | Thesis  | Organization                                   | . 27 |

| 2  | Anal | ysis of | Current Multimedia Extension Sets              | . 29 |

|    | 2.1  | Tables  | of Multimedia Extension Support for SWAR       | . 42 |

|    |      | 2.1.1   | Sources and Architectural Features             | . 44 |

|    |      | 2.1.2   | Arithmetic Instructions                        | . 45 |

|    |      | 2.1.3   | Shift and Rotate Instructions                  | . 67 |

|    |      | 2.1.4   | Bitwise-Logical and Bit-Reduction Instructions | . 70 |

|    |      | 2.1.5   | Conditionals                                   | . 73 |

|   |     |         | 1                                                              | Page |

|---|-----|---------|----------------------------------------------------------------|------|

|   |     | 2.1.6   | Data Movement, Replication, and Type Conversion Operations     | 88   |

|   |     | 2.1.7   | Data Extraction, Insertion, and Permutation Operations         | 90   |

|   |     | 2.1.8   | Interleaving Operations                                        | 96   |

|   |     | 2.1.9   | Catenating, Packing, and Unpacking Operations                  | 101  |

|   |     | 2.1.10  | Memory Access Instructions                                     | 105  |

|   |     | 2.1.11  | Cache Management Instructions                                  | 114  |

|   | 2.2 |         | ary of Multimedia Extension Sets neral-Purpose Microprocessors | 120  |

|   |     | 2.2.1   | MVI                                                            | 120  |

|   |     | 2.2.2   | PA-RISC MAX-1                                                  | 123  |

|   |     | 2.2.3   | PA-RISC MAX-2                                                  | 126  |

|   |     | 2.2.4   | MIPS-V                                                         | 128  |

|   |     | 2.2.5   | MDMX                                                           | 129  |

|   |     | 2.2.6   | AltiVec                                                        | 131  |

|   |     | 2.2.7   | VIS                                                            | 134  |

|   |     | 2.2.8   | MMX                                                            | 136  |

|   |     | 2.2.9   | 3DNow!                                                         | 137  |

|   |     | 2.2.10  | Enhanced 3DNow! and MMX                                        | 138  |

|   |     | 2.2.11  | 3DNow! Professional                                            | 139  |

|   |     | 2.2.12  | Extended MMX                                                   | 140  |

|   |     | 2.2.13  | SSE                                                            | 141  |

|   |     | 2.2.14  | SSE2                                                           | 142  |

|   | 2.3 | Other   | SWAR architectures                                             | 142  |

| 3 |     |         | f a General-Purpose<br>gramming Model                          | 147  |

|   | 3.1 | Relatio | onship to Previous Architectures                               | 149  |

|   | 3.2 | Relatio | onship to Previous Programming Models                          | 151  |

|   | 3.3 | The G   | eneral-Purpose SWAR Processing Model                           | 166  |

|   |     | 3.3.1   | Classification                                                 | 167  |

|   |      |         |                                                                | Page |

|---|------|---------|----------------------------------------------------------------|------|

|   |      | 3.3.2   | Data Representation                                            | 167  |

|   |      | 3.3.3   | Parallel Operations                                            | 175  |

|   | 3.4  | Prope   | rties of a Well-Designed High-Level Language for SWAR          | 191  |

|   | 3.5  | Develo  | opment of the Model                                            | 192  |

| 4 | Proc | of-Of-C | oncept Implementations of the Model                            | 195  |

|   | 4.1  | Proto   | type Libraries for SWAR Processing                             | 195  |

|   |      | 4.1.1   | libMMX                                                         | 195  |

|   |      | 4.1.2   | SWARlib                                                        | 196  |

|   | 4.2  | The S   | WARC Vector Language                                           | 199  |

|   |      | 4.2.1   | Type System                                                    | 200  |

|   |      | 4.2.2   | Control Constructs and Statements                              | 203  |

|   |      | 4.2.3   | Operators                                                      | 205  |

|   |      | 4.2.4   | An Example Function                                            | 208  |

|   | 4.3  | The S   | cc Compiler                                                    | 209  |

|   |      | 4.3.1   | Organization                                                   | 209  |

|   |      | 4.3.2   | The Front End                                                  | 210  |

|   |      | 4.3.3   | The Back End                                                   | 211  |

|   | 4.4  | Imple   | mentation of Compiler Optimizations For SWAR                   | 215  |

|   |      | 4.4.1   | Promotion Of Field Sizes                                       | 215  |

|   |      | 4.4.2   | Vector Algebraic Simplification and Bitwise Value Tracking     | 216  |

|   |      | 4.4.3   | Spacer Value Tracking and Simplification of Spacer Manipulatio | n218 |

|   | 4.5  | Comp    | arison with Concurrent Work                                    | 220  |

| 5 | Eval | uation  | of General-Purpose SWAR Model and Implementations              | 225  |

|   | 5.1  | An In   | teger Expression Validation Program                            | 225  |

|   | 5.2  | An In   | teger Benchmark — Subpixel Rendering                           | 227  |

|   | 5.3  | An In   | teger Emulation Benchmark — Gene Matching                      | 228  |

|   |      | 5.3.1   | Analysis of Results on AltiVec Target                          | 230  |

|   |      | 5.3.2   | Analysis of Results on MMX Target                              | 233  |

|    |                                            | Page |

|----|--------------------------------------------|------|

|    | 5.3.3 Analysis of Results on 3DNow! Target | 234  |

|    | 5.3.4 Analysis of Results on IA32 Target   | 235  |

|    | 5.4 A Floating-Point Benchmark — Linpack   | 235  |

| 6  | Conclusion                                 | 239  |

|    | 6.1 Future Research                        | 242  |

| LI | ST OF REFERENCES                           | 244  |

| A  | Historical Perspective                     | 261  |

| В  | Supported SWAR Extensions                  |      |

|    | in Commodity CPUs                          | 337  |

| С  | SWAR Instruction Mnemonics                 | 341  |

| D  | Scc Internal Pseudo-Operations             | 385  |

| Ε  | The Integer Expression Validation Program  | 389  |

| F  | The DNA Example Benchmark                  | 393  |

| G  | Numerical Results for DNA Benchmark        | 405  |

|    | G.1 Results on AltiVec Target              | 405  |

|    | G.2 Results for MMX Target                 | 406  |

|    | G.3 Results for 3DNow! Target              | 409  |

|    | G.4 Results for IA32 Target                | 409  |

| Н  | Linpack Performance                        | 417  |

|    | H.1 Results for 3DNow!                     | 417  |

|    | H.2 Results for AltiVec                    | 420  |

| VI | ${ m TA}$                                  | 422  |

# LIST OF TABLES

| Tabl | e                                                          | Page |

|------|------------------------------------------------------------|------|

| 2.1  | Comparison of Multimedia Instruction Set Extensions        | 46   |

| 2.2  | SWAR Addition Operations                                   | 50   |

| 2.3  | SWAR Subtraction Operations                                | 54   |

| 2.4  | Maximum and Minimum Operations                             | 58   |

| 2.5  | Multiplication Operations                                  | 62   |

| 2.6  | Combined Arithmetic Operations                             | 65   |

| 2.7  | Division and Advanced Arithmetic Operations                | 68   |

| 2.8  | Shift and Rotate Operations                                | 71   |

| 2.9  | Polymorphic Operations                                     | 74   |

| 2.10 | Condition Testing Operations                               | 79   |

| 2.11 | Conditional Flow Control Operations                        | 83   |

| 2.12 | Conditional Data Manipulation Operations                   | 86   |

| 2.13 | Data Movement, Replication, and Type Conversion Operations | 91   |

| 2.14 | Data Extraction, Insertion, and Permutation Operations     | 97   |

| 2.15 | Interleaving Operations                                    | 102  |

| 2.16 | Catenating, Packing, and Unpacking Operations              | 106  |

| 2.17 | Memory Access Operations                                   | 115  |

| 2.18 | Cache Management Operations                                | 119  |

| B.1  | Supported SWAR Extensions in Commodity CPUs                | 338  |

| C.1  | Comparison of Multimedia Instruction Set Extensions        | 342  |

| C.2  | SWAR Addition Operations                                   | 343  |

| C.3  | SWAR Subtraction Operations                                | 346  |

| C.4  | Maximum and Minimum Operations                             | 348  |

| C.5  | Multiplication Operations                                  | 349  |

| Tabl | le                                                           | Page |

|------|--------------------------------------------------------------|------|

| C.6  | Combined Arithmetic Operations                               | 352  |

| C.7  | Division and Advanced Arithmetic Operations                  | 354  |

| C.8  | Shift and Rotate Operations                                  | 355  |

| C.9  | Polymorphic Operations                                       | 357  |

| C.10 | Condition Testing Operations                                 | 359  |

| C.11 | Conditional Flow Control Operations                          | 364  |

| C.12 | Conditional Data Manipulation Operations                     | 366  |

| C.13 | B Data Movement, Replication, and Type Conversion Operations | 368  |

| C.14 | Data Extraction, Insertion, and Permutation Operations       | 371  |

| C.15 | Interleaving Operations                                      | 374  |

| C.16 | Catenating, Packing, and Unpacking Operations                | 377  |

| C.17 | Memory Access Operations                                     | 380  |

| C.18 | Cache Management Operations                                  | 383  |

| D.1  | Scc Internal Pseudo-operations                               | 386  |

| G.1  | AltiVec Trial Runs                                           | 407  |

| G.2  | MMX Trial Runs                                               | 410  |

| G.3  | 3DNow! Trial Runs                                            | 412  |

| G.4  | IA32 Trial Runs                                              | 415  |

| H.1  | Results for rolled C code                                    | 418  |

| H.2  | Results for SWARC code                                       | 419  |

| H.3  | Results for rolled C code                                    | 420  |

| H 4  | Results for SWARC code                                       | 191  |

# LIST OF FIGURES

| Figu | re                                 | Page |

|------|------------------------------------|------|

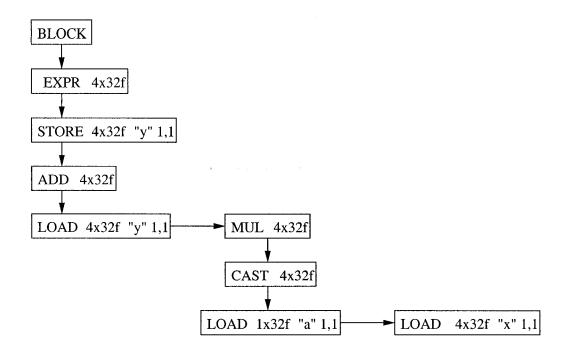

| 4.1  | IR tree for SWAR SAXPY             | 211  |

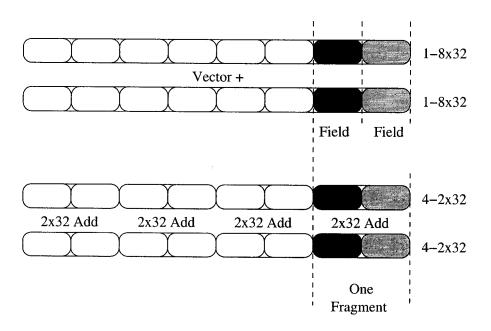

| 4.2  | Fragmentation of a Vector Addition | 212  |

#### NOMENCLATURE

fxbA partitioned entity with f fields of b bits each fxbsA partitioned entity with f signed fields of b bits each fxbuA partitioned entity with f unsigned fields of b bits each fxbfA partitioned entity with f floating point fields of b bits each Part Indicates a partitioned operand Scalar Indicates a partitioned operand with identical field values Element Indicates one field of a partitioned operand Single Indicates a partitionable register taken as a single unpartitioned value Immed Indicates an immediate operand encoded in the instruction itself Acc Indicates that the result will be added to the accumulator Acc Init Indicates that the result will be stored in the accumulator Acc Diff Indicates that the difference will be added to the accumulator Acc Sub Indicates that the result will be subtracted from the accumulator

#### ABSTRACT

Fisher, Randall James. Ph.D., Purdue University, May, 2003. General-Purpose SIMD Within A Register: Parallel Processing On Consumer Microprocessors. Major Professors: Henry G. Dietz and Leah H. Jamieson.

Recent extensions to microprocessor instruction sets are intended to speed-up multimedia algorithms by allowing SIMD parallel processing over multiple data fields within each processor register. These extensions, while effectively supporting hand-coding of some multimedia tasks, do not directly support a high-level parallel programming model. Unfortunately, the extensions vary widely across different processor families, making portability difficult to achieve. Even within one set of extensions, each operation is supported only for certain field widths, and the widths supported are different for different operations. This thesis will define a general-purpose SWAR (SIMD Within A Register) programming model. This model will be implemented for multiple target architectures: initially as compatible libraries, then as optimizing compilers accepting a simple high-level parallel language. The new SWAR libraries and compiler technology should enable a much wider range of applications to achieve speed-up through SIMD execution using COTS microprocessors.

### 1. INTRODUCTION

#### 1.1 Motivation

Modern commodity microprocessors employ a limited form of parallel processing in order to speed up multimedia algorithms. While these modified architectures are similar to certain traditional parallel processing models, they have unique and varied constraints on how they can be used. Traditional models of parallel processing are based on more powerful architectures and thus do not account for these constraints. To better reflect the capabilities and limitations of these new architectures, and to bridge the gaps between them, a new abstract model is required. We call this new processing model SWAR (SIMD Within A Register).

# 1.1.1 A Brief Introduction to Processing Models

To understand why previous abstract models are not sufficient, we need to have an understanding of these models and their purposes. Flynn's classification of processing systems [1] is useful in this endeavor, and we will use it to help denote the various processing models in this discussion. While we will often treat them as being interchangeable, computer architectures and the languages used to program them may actually be based on different processing models. In this discussion, we will differentiate between architectural and programming models as necessary. Also, these models are presented in an order that is not necessarily chronological, but should highlight their salient properties.

Sequential processors execute a single instruction on a single set of scalar operands at any given time. To reflect this fact, Flynn named this processing model SISD (Single Instruction stream, Single Data stream). This model is the basis for most

computers including the first microprocessor systems. While SISD systems are sufficient for many of the computing problems we encounter on a daily basis, they are too slow to be used to solve very large problems in a reasonable amount of time. A desire to improve upon this situation led to the development of new architectures and processing models.

Pipelined processors are SISD machines in which each instruction is executed in a single processing unit with multiple stages. The processor is set up like an assembly line with each stage performing one part of the total work needed to complete the instruction. An instruction can occupy only one stage of the pipeline at any given time, leaving the remaining stages available to other instructions. Thus, multiple instructions from an instruction stream can be in the pipeline simultaneously.

In mathematics, a vector is a single-dimensional, multi-element object. Vector programming models help programmers express operations on vectors more concisely than do scalar models. Many of these operations are applied to each of the vector's elements independently or cumulatively. For example, adding two vectors is equivalent to adding their elements in a pairwise manner. Vector programming models allow such operations to be expressed as a single operation on a vector rather than as a series of scalar operations on the vector's elements.

Vector processors were developed to minimize the costs associated with performing vector operations. They capitalize on the fact that most vector operations are repeated over many elements. For these operations, some of the pipeline execution stages need only be performed once for the entire vector. Thus, vector processors reduce execution time by removing redundancy in the execution of identical elementwise operations.

The simplest vector processors execute repetitive vector operations by sequentially running the vector elements through an ALU which performs an identical operation on each element. *Pipelined vector processors* allow multiple ALUs to be chained together to form an execution pipeline similar to that of a pipelined SISD processor. This

increases the performance of the processor by allowing multiple vector operations to not only share control stages but also to overlap in time.

While these vector processors can achieve significant speedup, they fail to fully exploit the available parallelism of vector code. This is because they perform each operation on only one set of corresponding elements at a time. Thus, in some sense, they are actually just improved SISD machines. To obtain better performance, processing models were developed in which work is performed on multiple parts of a problem simultaneously (i.e. in parallel). This is known as *parallel processing*.

These new processing models were more closely matched to the large, scientific problems which high-performance systems were intended to address than were the scalar models upon which sequential and simple vector processors were based. These problems included the modeling of physical phenomena such as weather and nuclear reactions and the analysis of observed data such as satellite photographs.

In these problems, physical environments or entities are represented by large data sets. For example, each datum may represent the value of some physical property at one of thousands of points within an environment at some given time. At each point, the predicted future value of this property is a function of its current value and its value at each of the neighboring points in multiple directions. Thus, solving these problems typically requires not only large amounts of computational power but also timely access to both local and neighboring point data.

Parallel processors are systems which are based on parallel processing models. These systems consist of multiple processing units which operate on multiple instruction streams simultaneously. Typically, these processing units are connected to form an array via one or more communications networks. These interconnection networks, which are sometimes referred to simply as the interconnect, allow point data to be passed between neighboring processing units in one or more dimensions. Thus, these systems were designed to be appropriate targets for large-scale scientific problems.

There are two major forms of parallelism which these systems exploit. *Control parallelism* refers to the separation of a problem into multiple independent sections

which can be executed simultaneously. Data parallelism refers to problems with a regular nature in which the same series of operations must be applied to multiple sets of data. Different processing models and architectures were developed to exploit these differing forms of parallelism.

MIMD (Multiple Instruction stream, Multiple Data stream) is a parallel processing model that was developed as a means of exploiting control parallelism in large problems. The computational nodes of a MIMD processor each execute a series of instructions which may differ from that of the other nodes. This allows each node to execute an independent section of the problem.

MIMD processors can simultaneously run multiple unrelated sections of code or multiple copies of identical code. This allows various programming models to be used to program these systems. For example, the MIMD programming model is based on the assumption that the problem is divided into pieces that may need to be synchronized occasionally, but are otherwise completely independent. The SPMD programming model (Single Program, Multiple Data) is similar, but is based on the assumption that the independent pieces are identical.

While MIMD processing is quite versatile, there is a cost associated with this flexibility due to the replication of both computational and control hardware. This makes MIMD relatively expensive. Other processing models were developed as a means of avoiding this cost while still benefitting from some form of parallelism.

One such model was SIMD (Single Instruction stream, Multiple Data stream), which was developed as a relatively inexpensive means of exploiting data parallelism. This is done by applying each operation simultaneously to as many data points as possible. Thus, a single instruction stream is executed on multiple data streams.

SIMD systems can be divided into vector-based and array-based systems. *Vector SIMD processors*, also called *vector parallel processors*, are single-dimensional SIMD processors designed to operate on vector data objects. *SIMD array processors* are SIMD architectures whose PEs are connected in shapes of two or more dimensions.

Vector SIMD processors execute repetitive vector element operations in a simultaneous fashion. With these processors, data is loaded into a set of vector registers which hold some fixed number of elements. Operations are then performed on some or all of these elements simultaneously. This allows the processor to take advantage of the data parallelism inherent in vector processing to achieve higher performance than non-parallel vector processors.

While vector processors shorten the time required to solve certain classes of problems, they are not well-adapted to solving large multi-dimensional problems efficiently. Array processors are better suited to these problems because they allow arrays to be processed with their coordinate systems intact. That is, these processors allow data from neighboring points in space to be stored in neighboring processing units.

A typical SIMD system has a single *control unit*, usually abbreviated CU, and an array of multiple processing units which are often called *processing elements* (PEs). The CU is responsible for reading a single stream of instructions from memory, decoding these instructions into control signals, and issuing the control signals to the PE array. Each PE executes the operation defined by the control signals on its own data stream. This data stream may be from a shared memory, but is usually from a memory which the PE holds privately.

Using a single controller makes SIMD systems inexpensive compared to the more general MIMD architectures in which the control unit is replicated for each of the PEs. Yet, for data parallel problems, SIMD retains the benefits of parallel processing associated with MIMD, thus giving it a higher performance to cost ratio.

One drawback of SIMD programming models is that they are severely limited when compared to MIMD models because every processor must execute exactly the same instruction simultaneously. This limits them to SPMD-style programs which are executed with every instruction synchronized.

This also makes the handling of high-level language control constructs, such as if statements, difficult. Typical SIMD systems have special hardware to turn PEs on and off (or equivalently, to block the side-effects of execution) depending on the local

conditions of the PE. If this hardware is not present, the executed program must be modified to nullify the effects of code that should not have been executed.

#### 1.1.2 Multimedia Extensions

Several programming and machine models have been developed to improve performance over traditional SISD computers. These were well-developed by the 1990s when manufacturers of commodity SISD microprocessors began experimenting with non-SISD architectures for multimedia processing.

Early work in this area focused on enhancing processors with on-chip graphical hardware. This was typically in the form of a handful of instructions for speeding common graphics operations. This included operations such as interpolating the position of non-end points on a line when only the endpoints were known and testing for the visibility of objects to determine if they should be drawn on the screen. These efforts were very limited, and not intended for general-purpose computing. However, they used methods that were later employed in implementing more general multimedia extensions.

In the 1990s, several manufacturers of commodity microprocessors began expanding their instruction set architectures with *multimedia extensions*. These were intended to speedup data parallel algorithms used in graphical and audio processing while keeping the amount of architectural modification required to implement them at a minimum. Of the processing models mentioned, the closest match to these goals was the vector parallel subset of SIMD. Thus, the designers of these multimedia extensions implemented them as sets of SIMD-like instructions.

When executed, these instructions are performed on multiple streams of data residing in a single CPU register. Thus, these extended architectures implement a form of SIMD processing. However, they differ from previous SIMD architectures because they have only one central processing unit (CPU) whose operation has been

altered to act like a CU with a set of PEs, rather than an actual set of PEs driven by a single, separate control unit.

This means that the entire set of PEs shares the CPU's single data path. Data can only be moved in and out of the PEs in the equivalent of block form from a single shared memory. Thus, a memory access moves a block of consecutive bits between a set of neighboring PEs and a single word in memory. This restriction is a significant limitation compared with typical SIMD architectures, which could load data from independent addresses or from private memories.

Data communication is also significantly different because there is often no equivalent to the communications networks employed in typical SIMD systems. Often SHIFT and ROTATE instructions are the only means available to move data between these pseudo-PEs. One communication type used in later SIMD architectures is a vector-indexed communication. This allows each PE to access data stored by some other PE, independent of the actions of the remaining PEs. Few multimedia architectures can perform such a generalized communication.

While not exactly SIMD, these SIMD-like extensions serve their intended purpose by allowing assembly language programmers to capture some of the potential speedup due to the data parallel nature of the targeted algorithms. Unfortunately, few of these extensions were designed with the intention of developing a complete processing model.

Usually, the registers and control logic used to implement these extensions needed to be enhanced to allow SIMD-like processing. This required considerable investment in the redesign and modification of the existing architecture. To minimize this investment while maximizing its perceived benefits, each of the extension sets has been targeted to support the multimedia algorithms that are believed to be most often used on its host platform. Thus, these extensions have limited functionality and tend to support only those data types and sizes which are normally used in multimedia.

Because of the variation in the architectures and the algorithms which are typically run on them, the instructions and data sizes supported often differ substantially between extension sets. Even within a single extension set, an instruction may exist to perform a particular operation on one size of data, but not on another size. This was intentionally done, based on the assumption that some operations are performed often on certain types of multimedia data, but rarely on others.

These variations and limitations are the primary problem with multimedia extensions, and limit their usefulness substantially. As a result, these extensions are sufficient for hand-coding architecture-specific, SIMD-parallel, multimedia operations at the assembly level, but are less useful beyond this scope. Variations between extension sets make code portability difficult, and the lack of consistent support for differing data sizes often forces format conversions between successive parallel operations. Finally, these extensions simply do not support certain data sizes and operations which may be useful to applications programmers in the future.

# 1.1.3 My Thesis

I believe that the set of applications which can benefit from these extensions is unknown and not limited to multimedia algorithms and data types. Also, that it is likely that multimedia extensions will continue to evolve, with some growing into more general systems and others dying out. Thus, not only will programmers need to be able to port code from one architecture to another, they will also want their code to take advantage of future capabilities without having to be rewritten for each new architecture.

Current programming models are either target-specific, based directly on some target's multimedia extensions, or based on programming models which do not match the capabilities of these architectures. These models are also unnecessarily limited to currently common data types and sizes. This ultimately limits their usefulness to those types of applications which we are able to foresee in the near future, and also prevents programmers from expressing algorithms which are best suited to non-standard data precisions. To move beyond the current situation, a general-purpose

programming model for the form of SIMD processing described above should be developed.

This form of parallelism, in which a single CPU register holds multiple data items that are operated on in a SIMD manner, is referred to as "microparallelism" by Alpern, Carter, and Gatlin [2], and belongs to a class of operation known as "sub-word processing." We will reserve the former term for any form of parallelism performed within a single register, including concepts such as single-register VLIW, and the latter term to mean any form of processing data which resides in less than a full machine word (e.g. byte operations on a 32-bit machine).

Thus, we shall consider the SIMD form of parallelism that this thesis addresses to be a subset of both microparallelism and sub-word processing. We refer to this form of processing as *SWAR* (SIMD Within A Register) [3].

While the limitations of multimedia extensions make it difficult to develop a consistent, portable, general-purpose SWAR programming model, they are not fatal. In fact, a generalized programming model can be developed which can target standard processor families with no SWAR-like extensions whatsoever.

It is my goal in this research to create a SWAR processing model which extends beyond the limits of current models, and to lay the groundwork for continued development of this form of parallel processing.

#### 1.2 Related Work

When this work was first proposed in 1997 [4], we were unaware of any other groups pursuing a high-level approach to general-purpose SWAR processing. Known support for SWAR processing was limited to assembly-level programming tools and high-level multimedia libraries. Since then, the situation has changed with various groups now performing related work.

While some of this work is similar to that presented in this thesis, to our knowledge there are still no other groups which take as broad an approach to SWAR processing as the one presented here. In this section, we discuss related work in the context of the pursuit of a general-purpose SWAR processing model.

These efforts can be separated into four primary types: software-only methods for SWAR processing, non-compiler tools which assist the programmer in the use of multimedia instructions, pre-written libraries which make use of multimedia instructions, and compiler support for SWAR processing. Some of this support was discussed in [5]. That work is updated and expanded here.

### 1.2.1 Software-only Methods

In his Doctoral Dissertation to the Royal Melbourne Institute of Technology [6], Mark Spieth presented the Single Processor Single Instruction Multiple Data processing model. This model is similar to that of SWAR, but is limited in several ways.

The primary goal of the research was to "explore the feasibility of the software only solution to the parallel implementation of arithmetic operations in single processors." This was a less ambitious goal than that proposed here which includes the use of SWAR hardware, expansion of the model to arbitrary data sizes, and the development of a fully portable programming model and related compiler technology.

The work by Spieth is a more complete theoretical treatment of the subset of the SWAR work dealing with the processing of packed standard integer data using software techniques on unenhanced hardware, primarily as it relates to image processing.

In his thesis, Spieth explored various representations of numeric information and provided a mathematical framework of packed number representations. The primary method explored was *aliasing*, in which the sign bit of each register data field is conceptually extended into the upper fields of the register and combined with the data in those fields. This causes the lower field data to affect the bit patterns stored in the upper fields. An unaliasing step is required to extract individual field data from the register.

Algorithms were provided for performing the operations Spieth considered to be valid for SPSIMD processing. These include addition, subtraction, constant multiplication and division, bit shifts, Boolean (i.e. bitwise logical), and conditionals within which are included minimum, maximum, and absolute value operations. This is a limited set compared to that of the SWAR model.

These algorithms were evaluated mathematically to determine the effects of aliasing on their operation and performance. It was found that aliasing places limits on the domains of the operands of these operations. Calculations of the theoretical speedup of these algorithms were also provided. These appear to be compared to software implementations of the same operation on unpacked data rather than against possible hardware implementations.

Spieth also examined the removal of the restrictions of the SPSIMD paradigm. These are the restriction of operation domains to prevent overflow from occurring and the restriction of result precisions to those of the source operands. Removal of the first restriction would allow the operand domain to encompass a larger range of values. Removal of the second restriction would allow intermediate calculations to increase in precision.

In the discussion of this examination, Spieth described split word processing where packed data is "split" into multiple packed words which each contain a subset of the packed data. This includes techniques that were discussed early in 1997 by Professor Dietz [3] and which are used extensively within the Scc compiler discussed later in this thesis. One of these techniques is the virtual spacer technique for implementing arithmetic operations that may overflow. Another is the general method of temporarily promoting packed data to a greater intermediate precision, performing operations at this precision, then repacking the data into its original precision.

Spieth found that removing the restrictions of the SPSIMD model using split word processing was effective, but subject to overhead, memory interface speed, and the set of assumptions one could make about the operands.

Tests of the effectiveness of the SPSIMD model were performed on several hand-coded image processing algorithms. This was done by comparing the results obtained using the SPSIMD version with those obtained for rolled and unrolled looped, sequential implementations as baselines. This was done on five different machines, running four different operating systems, and compiled with GCC or Borland C using their full set of optimizations.

Spieth also briefly discussed other criteria for evaluating SPSIMD processing including cost, convenience, and suitability. He specifically mentioned that he believed that the development of compiler extensions would improve the situation by providing packed data structures and parallel operations. This is one of the goals of my work and is beyond the scope of Spieth's.

A performance comparison of the methods used by Spieth versus those used in the compiler implementation described in this research would be an interesting future work. Also, Spieth's work should be further explored for possible alternative compiler implementations of SWAR operations which are not supported by hardware.

### 1.2.2 Non-compiler Tools

The lowest level of support for the use of multimedia extensions includes tools such as profilers and debuggers. Neither of these is in the realm of a programming model and can safely be ignored, but we will briefly mention some examples to convey a sense of their utility.

The VTune optimization package from Intel [7] provides programmers with performance tuning tools which analyze source code and offer advice for using Intel's multimedia extensions to improve it. This would typically be used in an ad hoc manner with programmers performing a coding cycle of writing code, profiling, then rewriting the code to try to get better performance. For some time, this was the only significant means of support provided by Intel for its multimedia extensions.

NuMega Technologies' SoftICE for Windows 95 and SoftICE for Windows NT [8] are debuggers which allow the disassembly of MMX instructions. These allow the programmer to use any available method of generating code which contains multimedia instructions, then debug or profile the resulting assembly code. It is likely that most multimedia-aware C/C++ compilation packages now include a debugger and/or integrated disassembler.

#### 1.2.3 Libraries

Pre-written libraries provide a high-level interface to a target's multimedia instructions. These libraries are usually both application- and target- specific, and perform common high-level operations which are comprised of multiple hardware instructions. They provide a means for applications programmers to exploit a target's multimedia extensions without being concerned with the details of the architecture; however, they typically do not address the issues of generality or portability.

Several application-specific libraries have been developed for MMX, including signal processing [9], image processing [10], speech recognition [11], and speech to text libraries[12]. A set of "Performance Libraries", to which the above libraries may belong, are included with Intel's Fortran and C++ compilers. These libraries are not intended to provide a general-purpose programming model, and support only specific data sizes.

Apple has adapted its core math libraries to make use of Motorola's AltiVec [13] extensions. They plan to rewrite their other libraries for this purpose in the future.

Sun Microsystems provides a C library called "mediaLib" [14] for the VIS extension set. mediaLib can be freely downloaded in binary form for certain platforms after a required licensing and non-disclosure agreement [15] is electronically accepted. Documentation for mediaLib is freely downloadable, and indicates that mediaLib is a high-level library which offers support for basic 8-, 16-, and 32-bit operations, as well as advanced functions such as FFTs.

The libSIMD project [16] is an attempt to define a portable math library for "commonly-used algorithms" across SIMD-enhanced and unenhanced architectures. The goal is to support "trigonometric, complex number, quaternion and FFT operations" on scalar, vector, and matrix objects. Functions are expected to be implemented using inline assembly code to access multimedia instructions and C code for portability to unenhanced architectures.

While plans for libSIMD are broad, its functionality is currently limited, consisting primarily of floating-point operations. Vectors and matrices appear to be limited to single fragment or sub-fragment lengths. The function listings in the documentation refer to 2-vectors, 3-vectors, and 4-vectors, while matrix functions operate on 2x2, 3x3, and 4x4 matrices.

libSIMD function arguments are objects in memory and results are stored to memory. Unless the compiler is able to perform optimizations across these procedures, possibly via inlining, then the memory access overhead will be too great to achieve significant speedup. Our decision to concentrate on a compiler rather than a general library was partially due to this fact.

The primary benefit of the libSIMD library would be portability of code between various multimedia-enhanced and unenhanced targets. However, this aspect seems to be insufficiently developed at this time as libSIMD is currently targeted only to AMD's 3DNow! extension set. This should change in the future as the author targets other multimedia extensions.

# 1.2.4 Compiler Support for SWAR

Current compiler support for SWAR processing consists primarily of various methods for exploiting multimedia extensions. This support falls into five major categories:

• Inline assembly and compiler intrinsics. This type of support gives the programmer low-level access to the instructions in the target's multimedia extension set. This allows the programmer to use multimedia instructions, but with

a minimum of compiler support. Programmers must maintain type and partitioning information themselves and choose the correct intrinsic to use based on this knowledge. In some cases, the compiler is able to optimize the resulting low-level code.

- Classes or types which represent a fragment. Compiler support of this type is also limited to low-level access, but type and partitioning information is tracked for the programmer via the type or class system of the source language. This information may be used by the compiler to ensure that the correct assembly instruction is executed based on the partitioning of the fragment operands.

- Automatic vectorization of loops. This type of support provides an abstract model which hides the use of extended instructions. With this type of support, well-known techniques are used to parallelize loops in existing code. The primary disadvantage is that loops must conform to certain forms for the compiler to recognize that they are parallelizable.

- Automatic vectorization of basic blocks. This type of support also provides an abstract model which hides the use of extended instructions. Here, code in a basic block is combined into operations on fragments. This is a more general approach than vectorization of loops because the code does not have to be in loop form to be vectorized. The primary disadvantage is the amount of work and space required to combine the code into vector operations.

- Languages with first-class vector objects. This type of support also provides an abstract model which hides the use of extended instructions. Here, the structure and semantics of the language indicate which operations can be automatically parallelized. This is more restrictive than automatic parallelization of basic blocks, but provides a concise method for describing vector operations.

We will now look at each of these categories in turn, and describe some of the related work which has been, or is being, conducted along these lines.

# Inline Assembly and Compiler Intrinsics

Inline assembly is low-level code for the target machine which is inserted into high-level language source code. This code is typically emitted directly into the assembly code generated by the high-level language compiler. This lets programmers use assembly language instructions of whose existence the compiler is unaware. In many cases this is the only form of support that the compiler provides for the use of extended instruction sets.

Compiler intrinsics are built-in functions which provide a function-call-like high-level interface to the target's machine instructions. Generally, these are trivial to implement and are usually just preprocessor macros which hide inlined assembly code which is used to execute a single instruction. These intrinsics are intended to provide access to instructions that the programmer would not otherwise be able to use, but generally do not provide functionality beyond the limits of the extended instruction set.

Inline assembly and compiler intrinsics operate at too low a level to be considered for a portable general-purpose SWAR processing model. However, this is often the starting point for other forms of support, so we will briefly survey some of the commercial compilers which support the use of multimedia instructions via intrinsics and/or macros.

Both Intel's Fortran [17] and C++ [18] compilers supply a set of intrinsics for their MMX, SSE, and SSE2 instruction sets. These intrinsics provide a means of describing the application of these instructions to objects in memory. The compiler is then responsible for register allocation and optimization of the resulting code.

Microsoft's Visual C++ version 5.0 compiler [19] also provides inline assembly support for MMX instructions as well the ability to disassemble code containing these instructions.

Metrowerks' CodeWarrior [20, 21] compiler provides inline assembly support for both MMX and AMD's 3DNow! instructions. This is one of several compilers of this product line which are targeted to different architectures. At least one version, CodeWarrior for Mac OS Professional Edition [22], supports AltiVec, although it isn't clear how.

Q Software Solutions LCC-Win32 compiler [23] also provides intrinsic support for MMX and 3DNow!. This compiler is an extension of the lcc compiler created by Fraser and Hanson for their text on compiler design [24].

The VectorC{PC} [25] C/C++ compiler by codeplay, Ltd., provides inline assembly support and intrinsics for the MMX, 3DNow!, and SSE extension sets. This compiler is intended primarily for the development of graphics-intensive games.

Green Hills Software makes an optimizing C/C++ compiler [26] which supports Motorola's AltiVec via a set of high-level intrinsics.

The VIS Software Developer's Kit (VSDK) [27] includes a set of macros for using Sun's VIS extensions. VSDK can be freely downloaded in binary form for certain platforms after a required licensing and non-disclosure agreement [28] is electronically accepted. The documentation for VSDK is part of the licensed package.

According to [29], C compilers which provide access via macros for Hewlett-Packard's MAX-2 extensions, Sun's VIS extensions, and the multimedia instructions of the MicroUnity and and Philips' Trimedia architectures have been available since the mid-1990's. The authors had suggested that a set of industry standard macros be developed. To the best of my knowledge, this has never been done.

### Classes or Types which Represent a Fragment

A vector *fragment* is the amount of parallel data than can reside in a single multimedia-enhanced register. Conceptually, long vectors of data can be broken into multiple smaller vectors which fit into a register. It is these small vectors that we refer to as a fragment.

Object-oriented classes or simple type definitions which represent a fragment can provide a first-class feel to these objects and the operations on them. To do this, class definitions include functions which overload common operators with parallel versions of the operation. Conversely, the use of non-class type definitions generally requires a modification to both the high-level language and the associated compiler to support parallel operations on these objects.

Several compilers support the use of multimedia extensions via class or type definitions. Usually, these fragment-based models are built on top of a set of intrinsics and support only the operations and partitionings native to the target's multimedia extension set. The following is a brief survey of a few of the compilers that provide this form of support.

The Intel C++ compiler includes class libraries for operating on MMX, SSE, and SSE2 fragments.

Free Pascal [30, 31] includes predefined array types for MMX and 3DNow!, and extends Pascal through what are essentially compiler directives to allow some first-class operations on these types.

Oxford Micro Devices' C compiler for its A236 Parallel Video DSP chip [32], which has instructions similar to MMX, provides predefined struct types for describing fragments. Arithmetic and comparison operations on these types are performed on a single fragment of data.

Motorola has developed an extension of the C programming language which includes a new "vector" type to represent a single AltiVec fragment. This extension is not intended to be portable to other architectures, and requires a modified version of the GNU C compiler [33], GCC, which generates AltiVec instructions to perform operations on these "vector" objects.

Green Hills Software's optimizing C/C++ compiler [26] also supports AltiVec via Motorola's "vector" extensions.

# Automatic Vectorization of Loops

Under strict conditions, and usually with hints from the programmer, some compilers are able to vectorize simple data-parallel loops. This support is in the early stages and is limited in the data types and operations that can occur in the body of the loop, although more advance techniques are under development. This development can be expected to follow that of Fortran loop manipulation and vectorization.

Intel's Fortran and C++ compilers provide automatic loop vectorization targeting the MMX, SSE [34], and SSE2 extension sets.

Metrowerks' CodeWarrior compiler provides vectorization for Intel's MMX and also for AMD's 3DNow! extensions [20]. Metrowerks is now owned by Motorola, so one would expect that support for Motorola's AltiVec extensions would be forthcoming. According to [13] this support is currently under development.

Green Hills Software's [26] C/C++ compiler supports AltiVec via automatic vectorization of loops.

Codeplay's VectorC{PC} C/C++ compiler performs automatic vectorization for MMX, 3DNow!, Enhanced 3DNow!, SSE, and SSE2 targets [35]. A separate version of this compiler targets the vector units of the Sony PlayStation2 [25].

The Portland Group's Workstation compilers for Fortran 77 [36], Fortran 90, C, and C++ [37] use a common core which supports automatic vectorization of loops for SSE-based targets.

Veridian Systems VAST/Parallel restructuring Fortran and C/C++ preprocessors [38] perform automatic loop vectorization and reordering as a front-end to a native compiler. Currently, these preprocessors only target the AltiVec multimedia extension set.

The VAST preprocessors have a long history, dating back to the mid-1980s when the Vector and Array Syntax Translator by Pacific Sierra Research Corporation was used to vectorize Fortran 200 code for the CDC Cyber 205 [39].

The VAST-F/AltiVec Fortran Preprocessor [40] "replaces vectorized Fortran loops with calls to VAST-generated C functions containing vector instructions." The VAST-C/AltiVec C Preprocessor [41] "automatically replaces loops in C programs with inline vector extensions (as defined by Motorola)."

These preprocessors generate C code in a manner similar to that of the Scc SWARC compiler discussed later in this work, but depend on Motorola's modified version of the GNU C compiler discussed previously.

According to [13], Absoft is also working on automatic vectorization of loops for Apple's Velocity Engine implementation of AltiVec. Their Pro Fortran compilers for Mac O/S 9 [42] and PPC/Linux [43], however, support AltiVec via precompiled Fortran 90/95 intrinsics and optimized benchmark and application-specific libraries. Automatic vectorization is only supported for the PPC/Linux version, and seems to be supported via Veridian's VAST-F/Vector preprocessors.

The VSUIF project at the University of Toronto [44] was conducted in the midto-late 1990's to add support for vector microprocessors to the SUIF compiler [45]. The goal of this project was to provide a high-level language programming model for using these architectures.

This compiler vectorizes loop-oriented, high-level language code into assembly code for the target architecture. The original target was the Torrent architecture [46, 47] which was then under development at the University of California at Berkeley. The designers planned to target Sun's UltraSPARC with VIS afterward, and a separate research effort was underway to create a SPARC code generator for SUIF [48]. This was intended to provide the back-end for VIS targets.

At the time [44] was written, DeVries and Lee had achieved some success vectorizing moderately complex code. They were still working on the handling of breaks and a method of classifying functions to determine if they would affect the vectorizability of loops when called. This work was to be validated using the UCB Torrent simulator before work to target the UltraSPARC was to begin.

We are unaware of the ultimate disposition of this work, although DeVries' Master's thesis is based on its implementation and performance [49]. While this project was intended to provide high-level support for vector processing, including SWAR targets, it takes the loop vectorization approach and does not treat vectors as first-class objects.

#### **Automatic Vectorization of Basic Blocks**

A more general approach to automatic vectorization is to search basic blocks for code which can be parallelized via the use of multimedia extensions. This allows not only loops to be vectorized, but also unrelated scalar code. This approach is also more general than parallelizing code based on first-class vector objects, because the statements which are automatically combined into vector fragments are not necessarily related.

Thus, this method is able to exploit a larger amount of parallelism than any other discussed. However, as with loop-vectorizing compilers, a compiler which vectorizes basic blocks is placed in the position of having to detect parallelism which is not explicitly described in the high-level language. This complex task requires a significant amount of time and space, more so than any other method of parallelization discussed here.

There are two groups known to be performing research in this area. The first is at the Massachusetts Institute of Technology's Laboratory for Computer Science. The other is at the University of Dortmund.

Work at MIT's Laboratory for Computer Science centers around what they term Superword Level Parallelism (SLP) [50]. This is defined as "short SIMD parallelism in which the operands and results of SIMD operations are packed in a storage location" [51].

The goal is to vectorize high-level sequential code throughout a basic block by detecting sets of single-valued *isomorphic statements* (statements which have the same

expression structure) and collecting them into a series of vector fragment operations. This "SLP algorithm" is proposed as an alternative to the vectorization of looped code. In fact, the SLP compiler unrolls loops in order to generate isomorphic sequential code that can be parallelized in this manner. The SLP detection algorithm is described in [51] and elaborated on in [52].

A later report [53] presents a simplified alternative to the SLP vectorizing algorithm; however, this algorithm exploits only a subset of the parallelism that the SLP detection algorithm can. Results presented in this report were based on the percentage of dynamic instructions eliminated from sequential benchmarks. These were calculated for the 128-bit AltiVec architecture and for larger hypothetical architectures via SUIF. Apparently, no actual timing information was gathered.

This project is based on the vectorization of pre-existing sequential code which may be marked-up with compiler hints to indicate the presence of hard-to-detect parallelism. As such, it does not conform to the SWAR vector programming model. However, it is probably a good complement to the SWAR model in that it seeks to find parallelizable expressions which are more general than SWAR vectors. Conceptually, one could fragment vector and array code, and apply the SLP detection algorithm to extract parallelism from the remaining scalar code.

Work at the University of Dortmund centers around "code selection" for media and embedded processors. The goal of this work is similar to that of the MIT group.

A compiler technique introduced in [54] and briefly described in [55] uses a data-flow graph (DFG) as an architecture-independent intermediate representation of a high-level language (i.e. C) source. This DFG is then walked using a pattern-matching algorithm which pre-assigns instructions to the parts of the tree. Branches which can be covered by a single one of the target's SWAR instructions are tracked. When the entire graph is covered, instructions are actually assigned with the use of SWAR instructions maximized.

The authors seem to be unaware of similar work performed in the parallel processing area. In [54] it is claimed that "SIMD instructions are so far not really exploited

by compilers for media processors. Taking advantage of such instructions is only possible, if processor-specific assembly routines or compiler intrinsics are used, resulting in low portability of software." This is despite the fact that the Scc compiler for the target-independent SWARC language was freely available for about two years before these papers were published and contemporary compilers such as Metrowerks' Code-Warrior [20] were capable of performing automatic vectorization of simple C language loops for multimedia-based targets.

# Languages with First-Class Vector Objects

Languages which provide first-class vector objects allow multi-fragment objects to be defined and operated on as a single entity. This has several benefits. First, it allows the programmer to express vector operations in a more concise manner than inline assembly, fragment-based types and classes, or automatically vectorized scalar code. Second, it allows portability between architectures by hiding their differences, such as supported partitionings and register sizes, from the programmer. Third, it allows the compiler to deal with issues such as code optimization rather than parallelism detection.

Existing compilers for languages which support first-class vector and array objects, such as Fortran 90, have been targeted to architectures which have multimedia extensions, but it is not clear that any of these convert first-class vector or array operations into multimedia instructions. For example, the literature for the Veridian Systems VAST-F/AltiVec Fortran preprocessor [40] never mentions any such support although loop vectorization is discussed.

We are aware of only one other research effort which specifically takes this approach to supporting SWAR architectures. This is the Vector Pascal project at the University of Glasgow. Vector Pascal [56] is an extension of the Pascal language to support first-class operations on vector and array objects targeted to multimedia-enhanced architectures.

In Vector Pascal, unary and binary operations can be performed on complete arrays or their subsections. Certain higher-level functions, such as sqrt, abs, and sin, are intrinsic to the language and can also operate on these objects.

Binary operations include modular and saturated addition and subtraction, other modular arithmetic operations such as multiplication, division, and exponentiation, and various other types of operations such as comparisons, shifts, and logicals. These operations assume an implied identity value if one is not given. This applies to operations on set expressions as well as numeric ones. For example, the Vector Pascal expression /a is equivalent in meaning to the expression 1/a for any value a.

For each of the binary operators there is an associated reduction operator. This applies the binary operation along the last dimension of its operand. These reductions reduce the rank of the operand by one with the exception of the scalar case in which they have no effect.

Objects of different rank can be operated on in mixed expressions with the restriction that, except for reductions, each variable in the expression must have rank less than or equal to that of the lvalue to which the expression's value will be assigned. Operands which have lower rank are replicated to match the rank of the lvalue. Operands of higher rank must be reduced in rank via one or more reduction operations.

User-defined functions which operate on a scalar object are automatically extended to apply to an array object of the same type in an element-wise manner. This mechanism allows the programmer to write functions that operate on both scalars and arrays of various sizes without having to parameterize the dimensions of its formal parameters.

One important aspect of SIMD programming that appears to be missing from Vector Pascal is the proper handling of parallel objects in the language's control constructs. No mention is made concerning if, or how, conditional constructs such as if statements and loops are handled when their conditional expressions are nonscalar. This is a significant issue which should be addressed in the design of a high-level SIMD language.

The Vector Pascal compiler uses the ILCG [57] code generation system in which a target description language is used to denote the specifics of the target architecture. The initial targets were the Intel 486 and Pentium with MMX. Currently Vector Pascal targets the "Intel 486, Pentium with MMX, and P3 and also the AMD K6." [56] It should be noted that these are all IA32-based architectures.

# 1.2.5 **Summary**

Software-only methods, such as Spieth's, cannot compete with those which take advantage of available SIMD instruction set extensions and can thus be rejected in most cases. These methods do, however, provide a level of portability between targets which cannot currently be obtained using multimedia extension sets only.

Low-level, high-performance libraries are closely related to their target architectures. These are often written to be inlined by a compiler and can thus be easily optimized. However, they do not provide portability between architectures and are thus insufficient for our model.

High-level libraries tend to be application-specific, intended to perform particular algorithms or operations for well-known problems. While typically having reasonably portable interfaces, these libraries are not intended for use in general-purpose algorithms and are usually too specialized for our purposes.

As a general rule, high-performance in library code comes at the price of non-portability. Thus, it is difficult, but not impossible, to develop a portable, high-performance, general-purpose library. Developing such a library would entail making a trade-off between these two competing factors.

Inline assembly and compiler intrinsics are directly related to their associated architectures, and thus operate at too low a level to be considered for a portable general-purpose programming model. However, they can be useful for code genera-

tion as they tend to ease the integration of unsupported hardware instructions into preexisting compilers.

Classes and types which represent a word-sized fragment of vector data also operate at too low a level to be considered for a general-purpose programming model. These are directly related to their associated hardware architectures, encoding the size of their registers, and often only provide access to the available hardware instructions. Thus, they generally do not present a portable programming model. This is not to say that classes and new types cannot provide a portable level of abstraction, only that current systems tend not to use these methods to their best advantage.

Compilers which perform automatic vectorization of scalar loops and basic blocks tend to be overly limited in their current capabilities. Most of the current set of vectorizing compilers are only capable of vectorizing simple loops that would be more succinctly expressed as first-class vector operations. More complex loops, those that cannot be expressed as vector operations, are typically too complex for these compilers to handle.

As current compiler writers learn more about, or reinvent, the work done in the high performance computing community over the last few decades, these compilers will become better at generating vectorized code from scalar sources. However, we should be developing programming models that make it easier to express complex operations, not high-performance compilers which optimize source code based on the wrong architectural model.

As part of the development of a new general-purpose SWAR programming model, the subject of this thesis, we have chosen to design a language with first-class vector objects because we believe this offers the best opportunity for performance gains over a large range of applications and target architectures.

Unlike any of the related work, this language allows both the precision of the data and the number of elements to differ from those supported by the hardware. It also provides a full, portable set of vector operations which are independent of the extended instructions available on any particular target. This language, SWARC,

will be discussed later in this work, and is, to the best of my knowledge, the only language which adheres to this generalized model.

# 1.3 Scope of Work

In this thesis, a new abstract model of parallel computation is developed which better reflects the capabilities and limitations of modern SWAR architectures than do current computational models. An example language based on this model is presented, as is a compiler for this language which uses various techniques to optimize code for these architectures. Performance metrics are also developed and employed to evaluate these implementations. This work should provide a starting point for future research and the development of practical programming languages for SWAR processing.

# 1.4 Thesis Organization

This thesis is organized as follows. Chapter 2 is a study of the multimedia extension sets available in commodity general-purpose microprocessors. Chapter 3 presents the general-purpose SWAR processing model. Chapter 4 describes the SWARC language which is based on the SWAR processing model and a proof-of-concept implementation of a SWARC compiler called Scc. Chapter 5 presents various evaluations of the defined SWAR model, the SWARC language, and the Scc compiler.

Maria de la Caración de Caraci

# 2. ANALYSIS OF CURRENT MULTIMEDIA EXTENSION SETS

A new abstract model of parallel computation is needed which will better reflect the capabilities and limitations of modern SWAR architectures than do current computational models. In order to develop a new model which adequately accounts for the capabilities and limitations of current SWAR architectures, it is necessary to have an understanding of the range of functionality which they support.

These architectures were created when commercial developers of microprocessors redesigned them to improve their performance on multimedia applications. This was done by extending their standard instruction sets with new sets of "multimedia instructions" which operate in a SIMD manner on parallel sections of their system data paths.

Each extension set was tailored to support the algorithms and applications which its designers believed to be most important to their clientele. Early extensions tended to be limited to instructions which perform operations that are frequently used in their particular target applications, and were not intended to present a complete parallel programming model to their users. Thus they failed to provide sufficient support for a viable SWAR processing model.

Because of the variation in their applications, the extensions meant to support them varied widely. However, some of these applications differ only in scope or quality, with the underlying algorithms being equivalent. Consequently, while each extension set is unique, its functionality may have aspects which are similar or equivalent to those of other extensions.

Later extensions are more complete, often including improvements which address problems with their ancestors' designs. Thus, a type of evolution is in play which may ultimately lead to relatively stable and complete sets of multimedia instructions.

Unfortunately, current extension sets still have limitations.

The range of support provided by these extensions still varies widely. The scope of these extensions also differs, with some including a large number of SWAR operations, while others include only a few. Support is still limited to data of standard sizes, and is still not consistent across these sizes. Also, instructions necessary for proper SIMD operation are often lacking or limited.

The primary goal of this phase of research was to determine the capabilities and limitations of the multimedia extension families which are available on current COTS (commodity, off-the-shelf) processors [4]. This analysis will be used as a basis for the design and implementation of the general-purpose SWAR programming model undertaken in later phases of the research. This is necessary to ensure that the developed model fairly reflects the common capabilities of current architectures.

This analysis should also be useful when deciding how an architecture's enhancements will be used within an implementation of the generalized model, and should foster insight into the possibility of code optimization based on a target architecture's enhanced features.